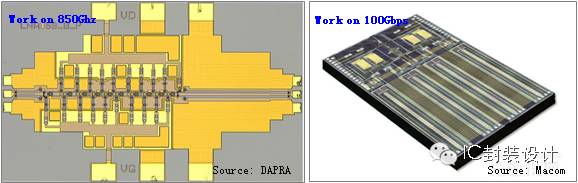

市場的需求,推動技術進步。今天物聯網、大數據、云計算等新一波浪潮來襲,萬物互聯必將產生海量的數據,數據的傳輸需要硬件來承載。信號的頻率越來越高,khz、Mhz、Ghz,目前Thz芯片已經慢慢的開始商用。數據傳輸的速率也越來越快,尤其是光傳輸技術的發展,光模塊的小型化,使得光通信技術慢慢從網絡產品普及到桌面產品上來。動輒幾十上百Gbps的傳輸速率,給SI設計帶來挑戰。如此高的頻率和速率,電信號在傳輸時,以前不太關注的芯片封裝,現在也必須考慮進來。

圖1

Thz芯片和100Gbps光芯片

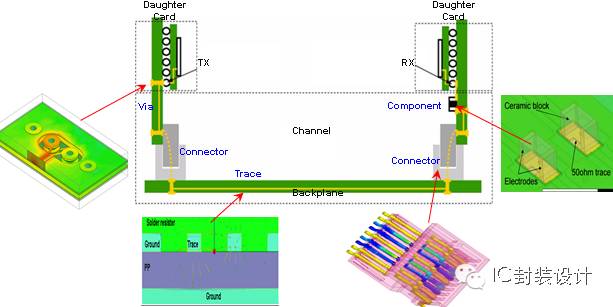

電性優化的目的,本質上來說就是最大提升傳輸效率,減少傳輸損耗。過去我們優化設計主要著眼于系統和PCB電路板這個級別,很少觸及到封裝和芯片。這個級別的仿真優化,主要集中在器件引腳、過孔、接插件等結構不連續的地方(圖2)。

圖2 系統級SI仿真優化

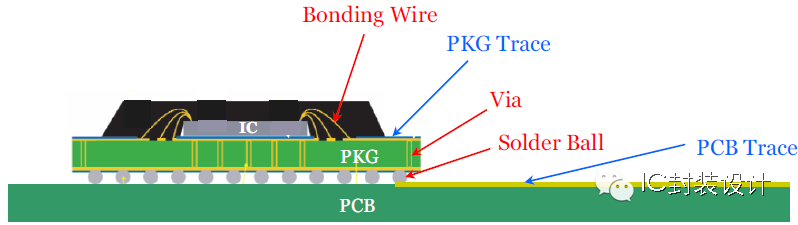

封裝是芯片到PCB電路板的過渡,這里的信號傳輸路徑處處存在著不連續(圖3),優化這些結構上的不連續點,使其保持電性上的連續,減少信號的反射,就是封裝SI優化的目的。接下來我們參照圖3的互聯結構,逐一簡要介紹各不連續點的優化方向,僅供參考。

圖3 封裝上的互聯結構

1. Bonding

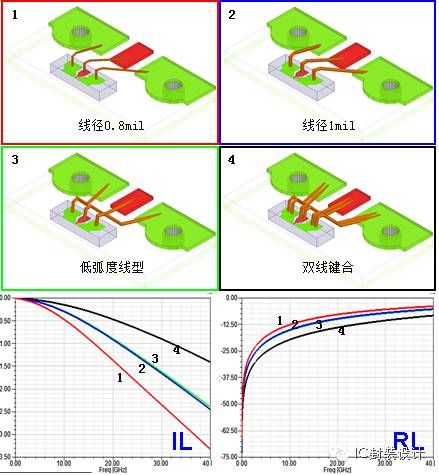

Wire

關于Bonding Wire的優化,主要涉及到信號和回流地的布置,金線的長度、直徑、線型、線數等。這里只對其他幾個參數再做討論。

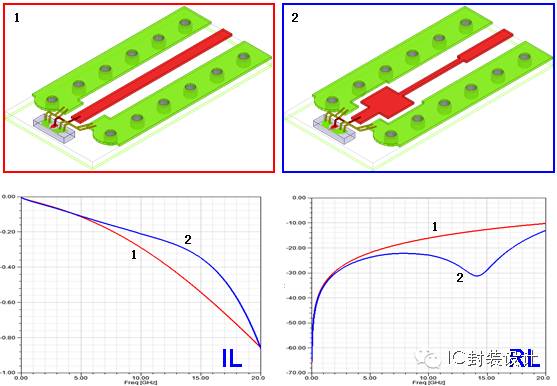

Bonding

Wire從芯片鍵合到載板,仿真結構建模如圖4;端口1設在芯片端,CPW結構,阻抗50Ohm;端口2設在載板端,GCPW結構,阻抗50Ohm;分別調整線徑,線型、線數三個因子,仿真頻率掃描0~40Ghz,后處理對比S21和S11參數。

圖4 Bonding wire對傳輸特性的影響

結論:

1.

金線直徑越大,傳輸特性越好;

2.

鍵合線弧度越低,傳輸特性越好;

3.

雙線鍵合,傳輸特性優于單線鍵合。

對于超高頻應用,僅僅通過調整以上參數來優化傳輸特性,依然滿足不了應用,鍵合線匹配就派上了用場。由于整個鍵合結構在一定頻率范圍內可以等效為電感,這樣我們就可根據射頻理論進行阻抗匹配。對比下面鍵合線匹配前后的傳輸特性,可以看出匹配在感興趣的頻段內,極大的優化了傳輸特性。

圖5 鍵合線匹配對傳輸特性的影響

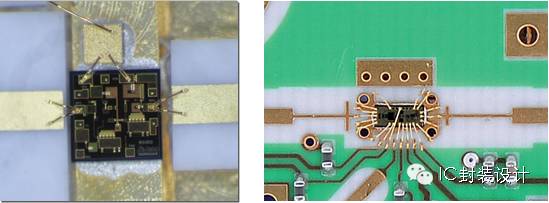

下圖是Wedge-Wedge低弧型雙線鍵合和金線阻抗匹配的應用案例。

圖6 低弧度雙線鍵合和金線阻抗匹配

2. PKG

Trace

PKG Trace封裝基板上的走線,由于這段是均勻傳輸結構,結構上沒有需要優化的點。我們更多關注在仿真時建模的準確性,考慮阻焊的厚度、Mold

compond,以及不同的基板工藝帶來的線路圖形差異。

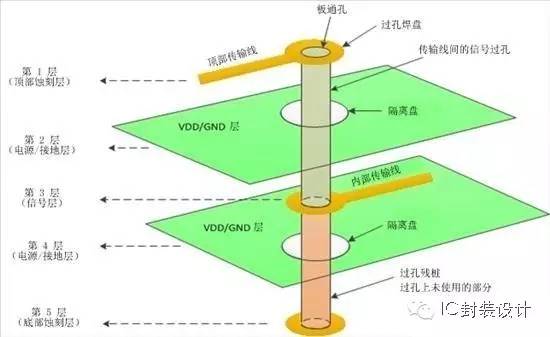

3.

Via

影響過孔傳輸特性的參數,包括孔大小、孔壁厚度、Pad大小、Anti-pad大小、回流地孔的數量、距離等等,網絡上關于PCB過孔優化的文章非常多,封裝基板過孔優化可以借鑒,建模時注意封裝基板工藝帶來的過孔結構差異(疊孔、填銅等)即可,其他不贅述。

圖7 Via結構

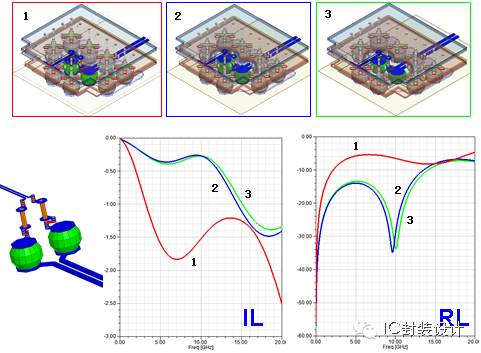

4. Solder

Ball

Solder Ball是封裝和PCB的互聯界面,因此這里的優化涉及到兩個部分——封裝基板和PCB電路板,涉及到的結構有Ball Pad,Solder

ball大小、高度、間距、回流Ball位置等。下圖,100Ohm差分阻抗走線,從封裝基板(4+2+4疊層結構)通過Via和Solder

ball過度到PCB上的100Ohm差分走線。

這里我們僅對基板和PCB電路板的Ball

Pad阻抗優化,以及降低Solder Ball的高度,仿真對比傳輸特性。由于Ball

Pad為處阻抗被拉低,我們通過挖空參考層的方法提高其阻抗(在“優化封裝以滿足SerDes應用鍵合線封裝規范”已有描述),減小突變;降低Solder

Ball的高度,減小回路電感。通過對比仿真結果我們可以看出,以上兩措施均對傳輸特性均有提高,尤其挖空Ball pad參考層的措施。

圖8 Solder Ball互聯界面結構及優化

5.

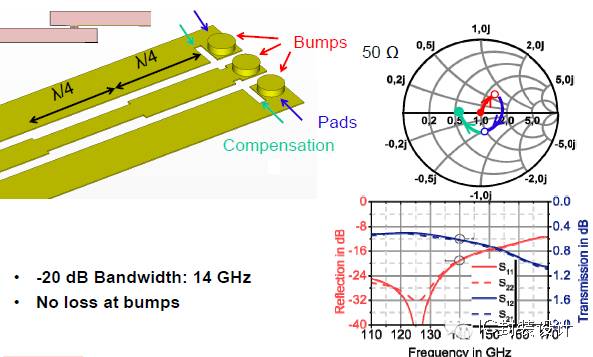

Bump

由于Flipchip的Bump與BGA的Solder

Ball結構相似,所以Flipchip可用同樣的方法優化傳輸特性。另外,Ball和Bump在高頻時呈感性,同樣可以用阻抗匹配的方法進行優化,下圖是優化案例。

圖9 Bump阻抗匹配

本文主要著眼于封裝結構的電性仿真,討論了Bonding Wire、Bump、PKG Trace、Via、Solder

Ball等對傳輸特性的影響。以上都是針對結構上的討論,對于封裝工藝、材料等對電性的影響,后面我們單獨開篇再作討論。

文章轉載于網路,如有侵權,聯系管理員刪除。