隨著摩爾定律逐漸逼近物理極限,傳統的二維平面封裝技術面臨諸多瓶頸,如布線密度不足、信號延遲增加以及功耗上升等問題。為此,三維堆疊封裝設計應運而生,作為一種先進的集成電路封裝方案,它通過將多個芯片或器件在垂直方向上進行堆疊和互連,實現了更高的集成度、更短的互連路徑以及更優的性能表現。三維堆疊封裝設計不僅代表了半導體封裝技術的一次革命性突破,還在人工智能、高性能計算、移動設備等領域展現出巨大潛力。本文將從技術原理、實現方式、優勢與挑戰、應用案例以及未來趨勢等方面,全面解析三維堆疊封裝設計,幫助讀者深入理解這一關鍵技術如何推動電子行業的創新。

三維堆疊封裝設計的核心在于通過垂直堆疊多個芯片層,利用硅通孔(TSV)等技術實現層間互連,從而在有限的空間內實現更高的功能密度。與傳統的二維封裝相比,這種設計能夠顯著縮短信號傳輸距離,降低功耗,并提升整體系統的可靠性。例如,在智能手機和服務器中,三維堆疊封裝可以集成處理器、內存和傳感器等多種組件,實現更高效的數據處理。然而,這一技術也面臨著熱管理、制造成本和工藝復雜性等挑戰。本文將系統性地探討這些方面,為讀者提供一個全面的技術視角。

一、三維堆疊封裝設計的基本概念與背景

三維堆疊封裝設計是一種將多個半導體芯片或器件在三維空間內垂直堆疊并互連的先進封裝技術。它起源于20世紀末,隨著集成電路尺寸的不斷縮小,傳統封裝方式在性能提升上遇到瓶頸。二維封裝通常依賴于平面布線,導致互連長度增加,信號延遲和功耗上升。而三維堆疊封裝通過垂直集成,將不同功能的芯片(如邏輯芯片、存儲芯片和傳感器)堆疊在一起,形成緊湊的模塊,從而克服了這些限制。

這種設計的背景與半導體行業的發展緊密相關。早期,封裝技術主要關注保護和連接芯片,但隨著電子設備向小型化、高性能化發展,封裝的作用逐漸擴展到提升系統整體性能。三維堆疊封裝的興起得益于多種技術的進步,例如微細加工技術、材料科學和熱管理方案。其中,硅通孔(TSV)技術是關鍵推動力,它通過在硅基板上制作垂直通道,實現芯片層間的電氣連接。TSV技術不僅減少了互連長度,還提高了信號傳輸速度,使得三維堆疊封裝在高性能計算和移動設備中廣泛應用。

從行業角度來看,三維堆疊封裝設計已成為先進封裝市場的重要組成部分。根據市場研究數據,全球三維堆疊封裝市場預計在未來幾年內保持高速增長,主要驅動力來自5G通信、人工智能和物聯網等新興領域。這種設計不僅提升了芯片性能,還降低了系統成本,因為它允許使用不同工藝節點的芯片進行集成,從而優化資源利用。例如,在內存堆疊中,三維封裝可以將DRAM和NAND閃存堆疊在一起,實現更高的帶寬和能效。總之,三維堆疊封裝設計代表了封裝技術從簡單保護向系統集成轉型的重要里程碑,為未來電子設備的發展奠定了基礎。

二、三維堆疊封裝設計的技術原理與實現方式

三維堆疊封裝設計的技術原理基于垂直集成和層間互連,其核心是通過將多個芯片或器件堆疊在一起,并利用先進互連技術實現高效的數據交換。這種設計的關鍵在于減少互連距離,從而降低信號延遲、功耗和噪聲。實現三維堆疊封裝的主要方式包括芯片堆疊、硅中介層和硅通孔(TSV)技術。

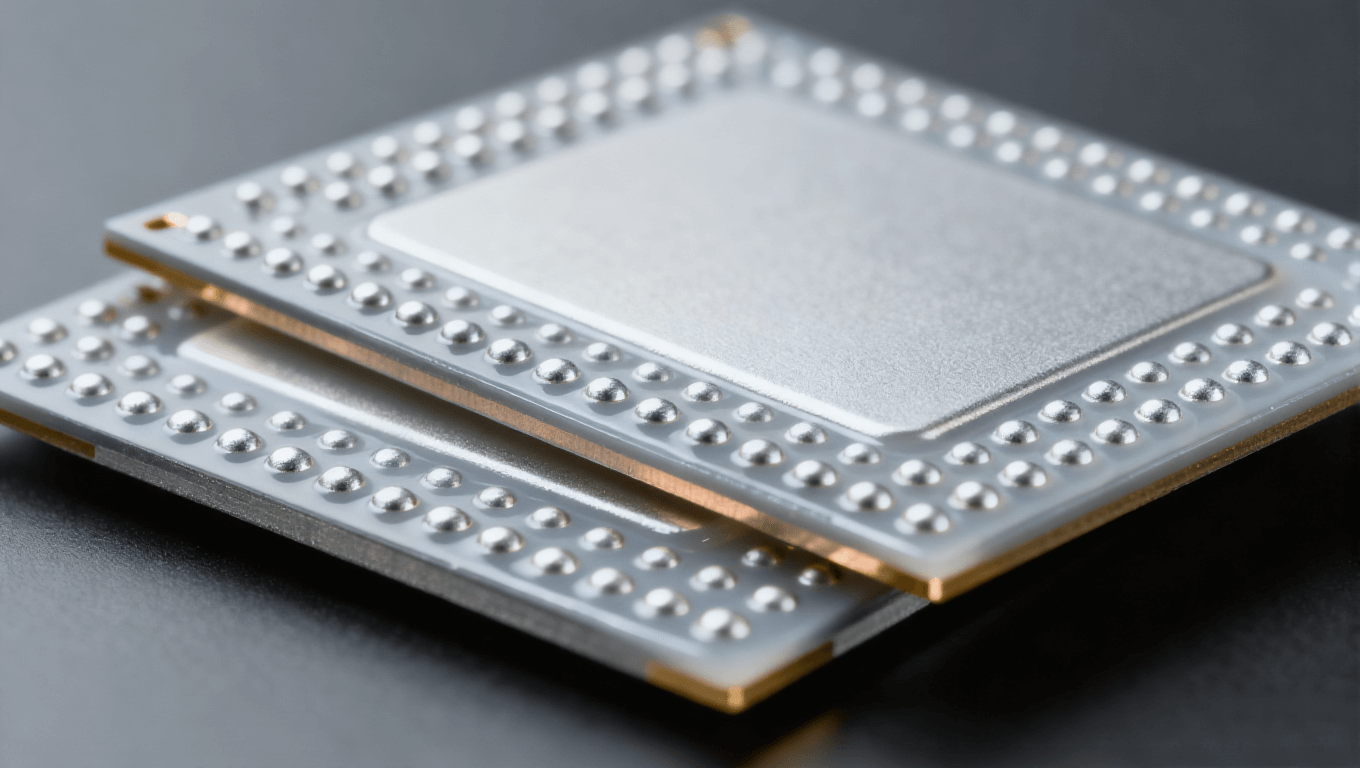

首先,芯片堆疊是三維封裝的基礎形式,它涉及將多個芯片垂直堆疊并通過焊接或粘合材料固定。堆疊方式可以分為同質堆疊和異質堆疊:同質堆疊指堆疊相同類型的芯片,如多個內存芯片;異質堆疊則集成不同功能的芯片,例如將處理器、內存和傳感器組合在一起。異質堆疊更復雜,但能實現更高的系統集成度。在堆疊過程中,芯片之間的間隙通常填充有導熱材料,以幫助散熱,同時使用微凸塊或銅柱進行電氣連接。

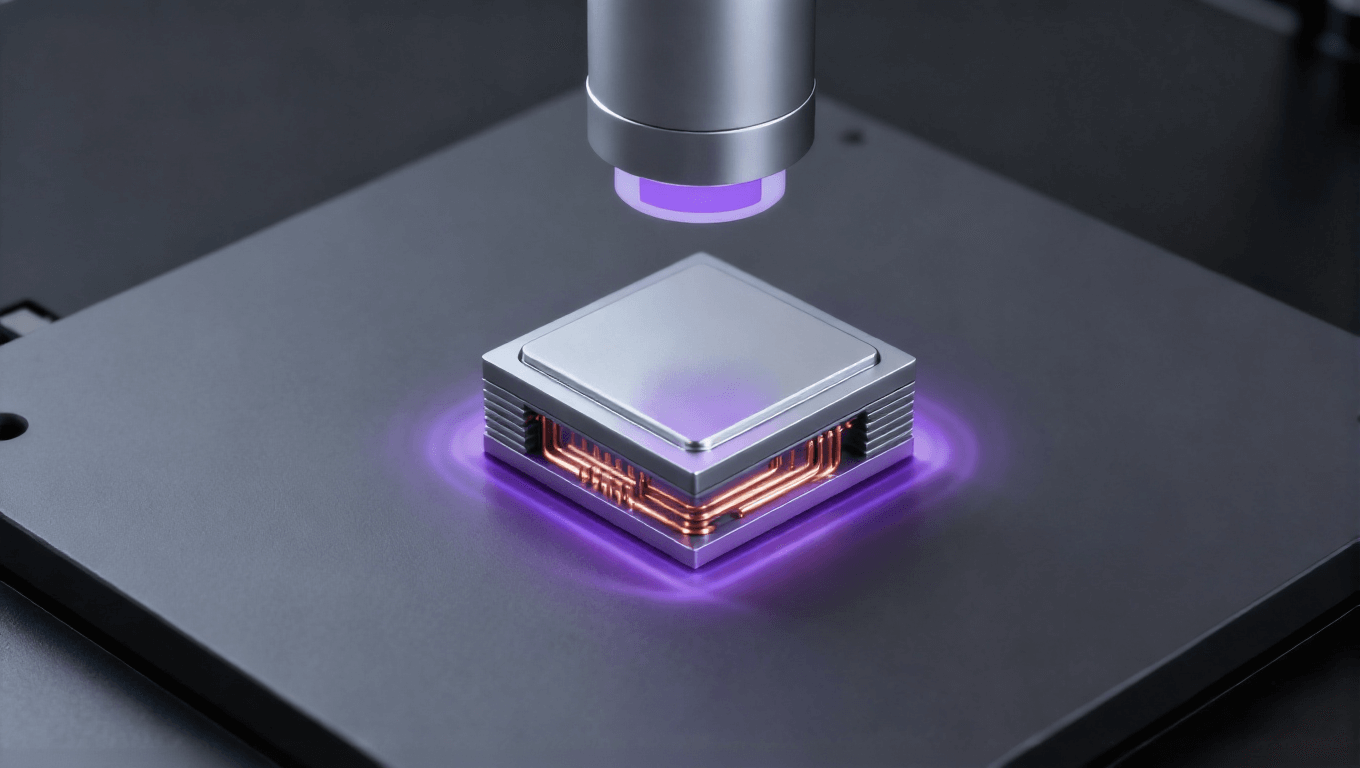

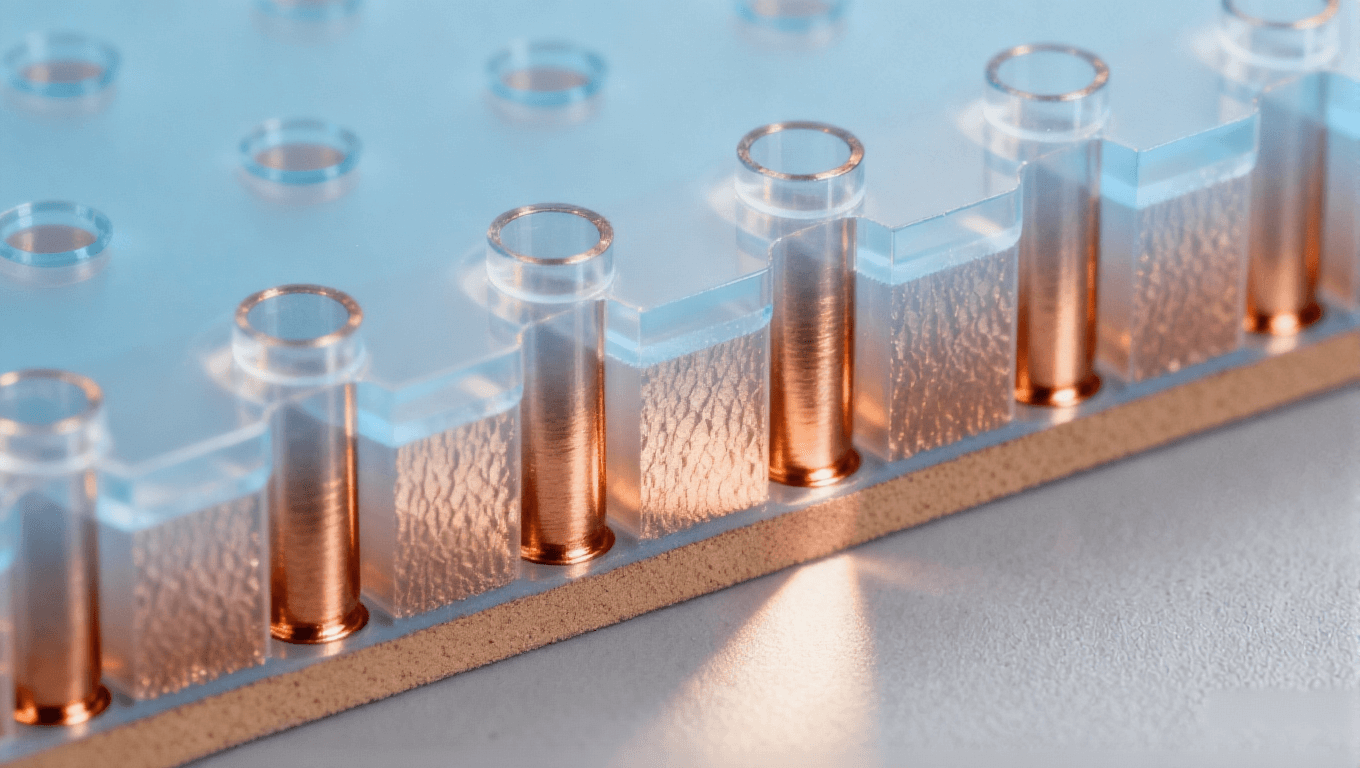

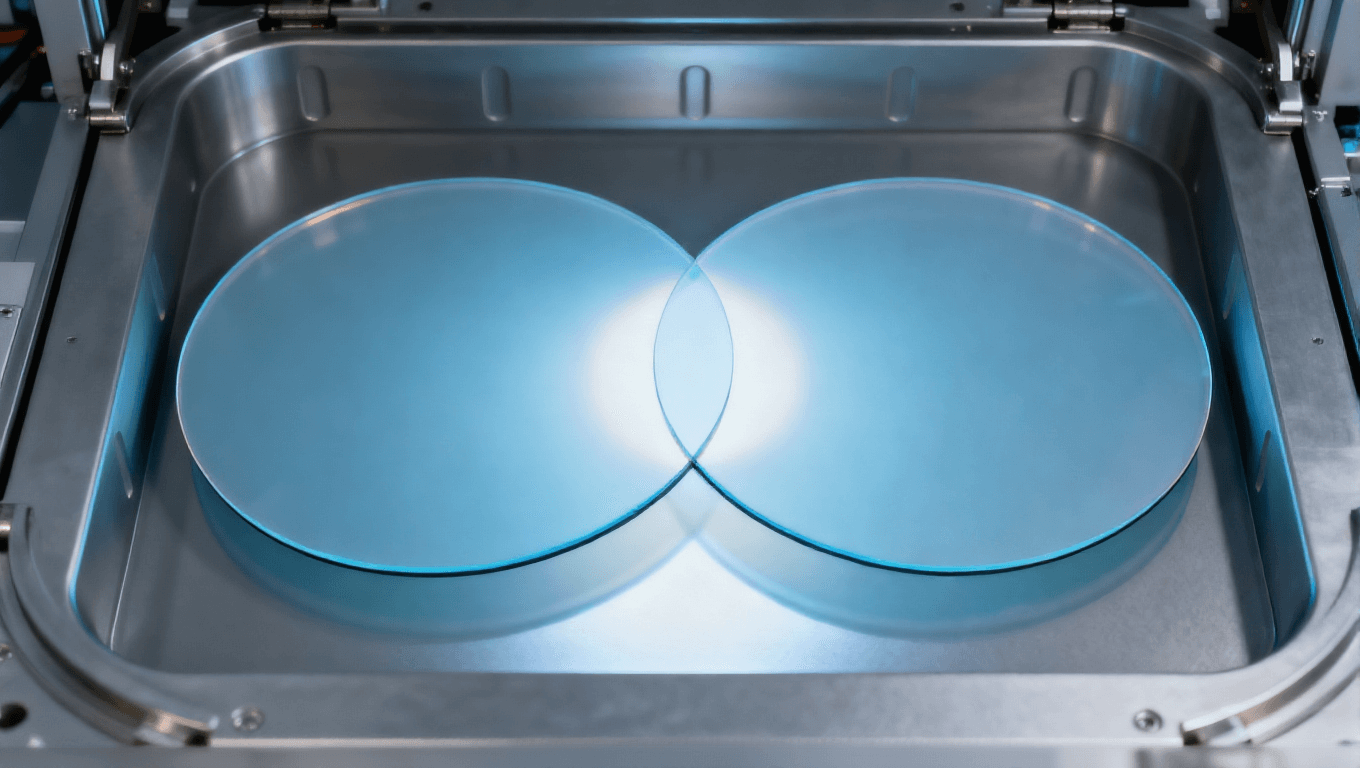

其次,硅通孔(TSV)技術是實現層間互連的核心手段。TSV是一種在硅基板上制作的垂直通道,內部填充導電材料(如銅),用于連接堆疊芯片的不同層。TSV的直徑通常在幾微米到幾十微米之間,深度可達數百微米,其制造過程涉及深反應離子刻蝕、電鍍和化學機械拋光等步驟。TSV技術的主要優勢在于它提供了最短的互連路徑,顯著提升了信號傳輸速度。例如,在三維堆疊內存中,TSV可以將多個DRAM層連接起來,實現比傳統二維封裝更高的帶寬和更低功耗。此外,TSV還能減少寄生電容和電感,進一步提高電路性能。

除了TSV,硅中介層是另一種常見的實現方式。硅中介層是一種位于堆疊芯片之間的薄硅片,上面布有互連線路,用于路由信號和電源。中介層可以通過TSV與上下芯片連接,形成一個完整的三維系統。這種方式特別適用于集成不同工藝節點的芯片,因為它提供了靈活的布線方案。例如,在高性能計算中,硅中介層可以將多個處理器和內存芯片集成在一起,實現高效的數據交換。

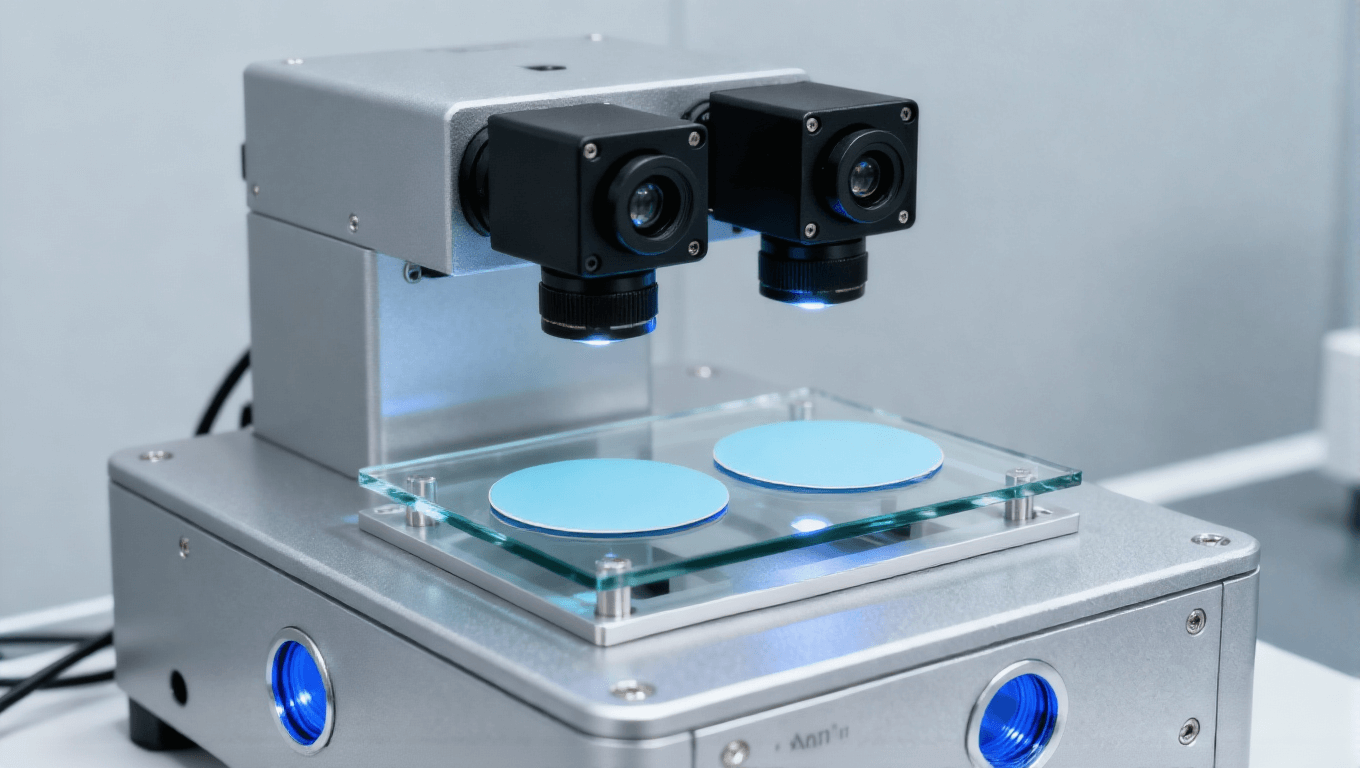

三維堆疊封裝的實現還涉及多個工藝步驟,包括芯片減薄、對準鍵合和測試。芯片減薄是通過研磨或化學方法將芯片厚度降低到幾十微米,以減少堆疊高度和改善熱管理。對準鍵合則確保芯片在堆疊時精確對齊,常用方法包括熱壓鍵合和激光鍵合。測試環節在制造過程中至關重要,因為三維堆疊結構的復雜性使得故障檢測和修復更具挑戰性。總體而言,三維堆疊封裝設計的實現依賴于多學科技術的融合,從材料工程到精密制造,每一步都需優化以確保可靠性和性能。

三、三維堆疊封裝設計的優勢與挑戰

三維堆疊封裝設計以其獨特的垂直集成方式,帶來了諸多優勢,但也面臨一系列技術挑戰。理解這些優勢與挑戰,對于推動該技術的廣泛應用至關重要。

優勢方面,首先,三維堆疊封裝顯著提升了集成密度和性能。通過垂直堆疊,它可以在相同的占地面積內容納更多芯片,從而實現更高的功能密度。這在移動設備和可穿戴設備中尤為重要,因為空間有限。例如,在智能手機中,三維堆疊封裝可以將應用處理器、內存和射頻芯片集成在一個模塊中,減小主板尺寸并提升處理速度。其次,這種設計縮短了互連長度,降低了信號延遲和功耗。根據研究,三維堆疊封裝的互連長度比二維封裝縮短了50%以上,這使得數據傳輸速度更快,尤其在高速計算應用中,如人工智能和數據中心服務器。此外,三維堆疊封裝支持異質集成,允許將不同工藝節點和材料的芯片組合在一起,優化系統性能。例如,將先進的邏輯芯片與成熟的存儲芯片堆疊,可以降低成本并提高能效。最后,這種設計還提升了系統的可靠性和靈活性,因為它可以通過冗余設計減少單點故障,并適應多種應用場景。

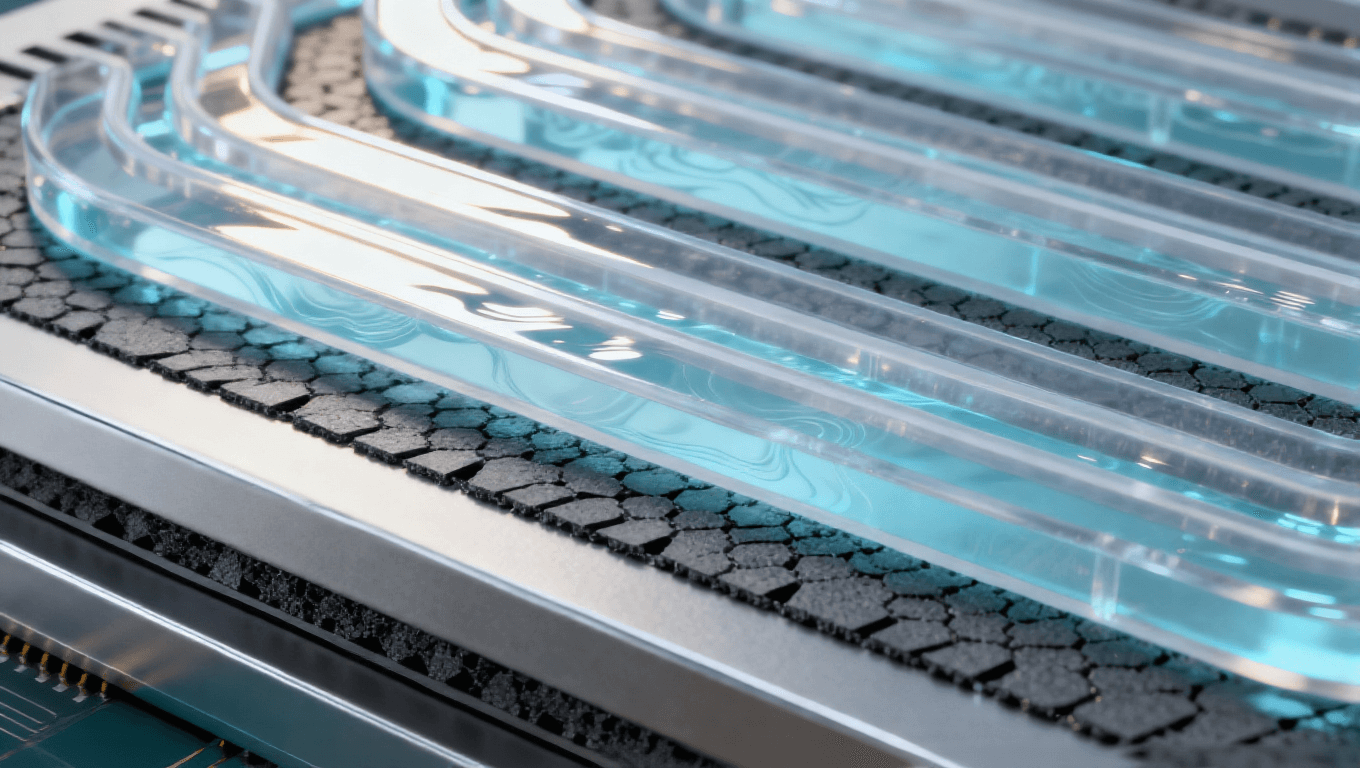

然而,三維堆疊封裝設計也面臨不少挑戰。熱管理是首要問題,因為堆疊結構會導致熱量在垂直方向積聚,容易引發過熱和性能下降。芯片之間的間隙小,散熱路徑有限,這就需要創新的熱管理方案,如集成微流體冷卻或使用高導熱材料。另一個挑戰是制造成本和工藝復雜性。三維堆疊涉及多個精密步驟,如TSV制造和芯片鍵合,這些過程需要高精度設備和高純度材料,導致成本上升。據行業估計,三維堆疊封裝的制造成本比傳統封裝高出30%-50%,這限制了其在低成本應用中的普及。此外,信號完整性和電源完整性也是關鍵問題。堆疊結構中的互連可能引入噪聲和串擾,影響電路性能。設計時需采用屏蔽技術和優化布線來解決這些問題。

測試和可靠性同樣是三維堆疊封裝的挑戰。由于堆疊結構復雜,傳統測試方法可能無法全面檢測故障,需要開發新的測試策略,如內置自測試(BIST)和三維掃描鏈。可靠性方面,堆疊芯片可能因熱膨脹系數不匹配而產生機械應力,導致長期失效。因此,材料選擇和結構設計需充分考慮耐久性。盡管存在這些挑戰,但通過持續研發和跨行業合作,三維堆疊封裝設計正逐步克服障礙,成為未來電子系統的關鍵。

四、三維堆疊封裝設計的應用領域

三維堆疊封裝設計因其高密度集成和性能優勢,在多個領域得到廣泛應用,從消費電子到高端計算,都展現出巨大潛力。以下是幾個主要應用領域的詳細分析。

在移動設備和消費電子領域,三維堆疊封裝已成為提升設備性能的關鍵技術。智能手機、平板電腦和可穿戴設備需要小型化、高性能的芯片模塊。例如,蘋果的A系列芯片和三星的存儲器模塊采用三維堆疊設計,將處理器與內存堆疊在一起,實現更快的處理速度和更長的電池壽命。這種設計不僅減小了設備尺寸,還支持多功能集成,如將圖像傳感器與處理芯片堆疊,提升相機性能。在5G時代,三維堆疊封裝還能集成射頻前端模塊,提高通信效率,滿足高速數據傳輸需求。

高性能計算和人工智能是另一個重要應用領域。在這些應用中,數據處理速度和能效至關重要。三維堆疊封裝允許將多個CPU、GPU和內存芯片堆疊在一起,形成高效的計算單元。例如,在服務器和超級計算機中,三維堆疊可以大幅提升并行處理能力,支持復雜的人工智能算法和機器學習任務。英偉達的GPU和英特爾的處理器已采用三維堆疊技術,通過TSV實現高帶寬內存(HBM)集成,顯著加速數據密集型應用。此外,在邊緣計算中,三維堆疊封裝幫助實現緊湊而強大的處理節點,適用于自動駕駛和工業物聯網。

存儲領域也廣泛采用三維堆疊封裝技術。NAND閃存和DRAM的內存堆疊已成為行業標準,通過垂直堆疊多個存儲層,實現更高的容量和更快的讀寫速度。例如,三星和SK海力士的三維NAND閃存產品堆疊了數十甚至上百層,大幅提升了存儲密度,同時降低了每比特成本。在固態硬盤(SSD)中,這種設計支持更高的IOPS(每秒輸入輸出操作數),滿足大數據存儲需求。此外,三維堆疊封裝在傳感器和MEMS(微機電系統)中也有應用,如將運動傳感器與處理芯片堆疊,用于智能家居和醫療設備,實現實時數據采集和處理。

總之,三維堆疊封裝設計的應用正不斷擴展,推動電子設備向更智能、更高效的方向發展。隨著技術的成熟,它有望在更多領域,如汽車電子和航空航天,發揮重要作用。

五、三維堆疊封裝設計的未來發展趨勢

三維堆疊封裝設計作為半導體行業的前沿技術,其未來發展將受到多種趨勢的驅動,包括材料創新、工藝優化和新應用拓展。預計在未來十年,這一技術將繼續演進,帶來更多突破。

首先,材料科學將是推動三維堆疊封裝發展的關鍵因素。目前,硅基材料主導TSV和中介層技術,但研究人員正探索使用新型材料,如碳納米管和石墨烯,以進一步提高導電性和熱管理性能。這些材料具有更高的熱導率和電導率,可以幫助解決堆疊結構中的散熱問題。此外,先進封裝材料如低介電常數(low-k)介質和高溫粘合劑將提升互連可靠性和信號完整性。例如,開發柔性基板材料可能使三維堆疊封裝適用于可彎曲電子設備,如柔性顯示屏和可穿戴傳感器。

其次,工藝優化和自動化將降低三維堆疊封裝的制造成本并提高 (良率)。隨著半導體設備精度的提升,TSV制造和芯片鍵合過程將變得更加高效和可靠。人工智能和機器學習技術在制造中的應用,可以實時監控工藝參數,預測故障,并優化生產流程。例如,通過AI驅動的檢測系統,可以快速識別堆疊過程中的對準誤差,減少廢品率。同時,三維堆疊封裝可能與其他先進封裝技術融合,如扇出型封裝(Fan-Out)和系統級封裝(SiP),形成混合解決方案,以平衡性能和成本。據行業預測,到2030年,三維堆疊封裝的成本可能下降20%-30%,使其在更廣泛的市場中普及。

應用方面,三維堆疊封裝將在新興領域發揮更大作用。在量子計算中,這種設計可以用于堆疊量子比特芯片,實現更復雜的量子電路;在生物電子中,它可以集成傳感器和處理單元,用于可植入醫療設備。此外,可持續發展趨勢將推動三維堆疊封裝向更環保的方向發展,例如使用可回收材料和低能耗制造工藝。總體而言,三維堆疊封裝設計的未來充滿機遇,它將與摩爾定律的延伸相輔相成,助力電子行業應對性能、尺寸和能效的挑戰。

三維堆疊封裝設計是半導體封裝技術的一次重大革新,它通過垂直堆疊和高效互連,實現了高密度集成、性能提升和尺寸縮小。從技術原理到應用實踐,這一設計展示了其在移動設備、高性能計算和存儲領域的巨大價值。盡管面臨熱管理、制造成本和可靠性等挑戰,但通過持續創新,這些障礙正逐步被克服。未來,隨著材料、工藝和應用的不斷拓展,三維堆疊封裝設計有望成為電子系統的核心,推動行業向更智能、更可持續的方向發展。