一、引言:電路板金屬化工藝的 “精度革命”

電路板作為核心載體,其制造精度直接決定了設備性能。從早期的通孔插裝技術到如今的表面貼裝技術,電路板的線寬已從毫米級縮減至微米級,甚至納米級,而這一演進背后,金屬化工藝的升級是關鍵支撐。

傳統電路板金屬化主要依賴電鍍、物理氣相沉積(PVD)等技術,但隨著 5G 基站、AI 服務器、折疊屏手機等高端設備對 “超細線路(線寬<20μm)”“微小通孔(孔徑<50μm)”“深寬比>10:1 溝槽” 的需求激增,傳統工藝逐漸暴露短板 —— 電鍍易出現 “邊緣厚、中心薄” 的沉積不均問題,PVD 在復雜結構表面的覆蓋性差,難以滿足高精度、高可靠性的制造要求。

正是在這一背景下,原子層沉積電路板金屬化工藝憑借 “原子級精度”“超高均勻性” 的獨特優勢,成為解鎖高密度電路板制造的核心技術。它不僅能解決傳統工藝的痛點,更推動電路板向 “三維集成”“柔性化” 方向發展,為高端電子制造注入新動能。

二、原子層沉積電路板金屬化工藝:原理與核心流程

要理解該工藝為何能實現 “原子級控制”,需先拆解其底層原理 —— 它并非傳統的 “批量沉積”,而是通過 “自限制化學反應” 實現 “逐層生長”,每一步都精準控制原子的沉積量,最終形成均勻、致密的金屬薄膜。

(一)核心原理:“四步循環” 實現原子級生長

原子層沉積(ALD)的本質是兩種或多種化學前驅體在基材表面交替發生反應,利用 “化學吸附飽和性” 實現自限制,具體流程可分為四步:

1. 前驅體吸附:精準 “錨定” 基材表面

向密封的反應腔室中通入第一種金屬前驅體(如用于銅金屬化的 Cu (hfac)?、用于銀金屬化的 Ag (fod)),這些前驅體分子會通過化學鍵或范德華力,均勻吸附在電路板基材(如 FR-4 樹脂、聚酰亞胺柔性基板)表面。由于基材表面的活性位點有限,前驅體分子吸附達到飽和后便不再增加,形成單分子層,這一步直接決定了后續沉積的均勻性。

2. 惰性氣體清洗:排除 “干擾因素”

通入惰性氣體(如氮氣、氬氣)吹掃反應腔室,將未吸附的多余前驅體和少量副產物徹底排出。這一步是 ALD 與其他沉積工藝的關鍵區別 —— 若不清洗,殘留的前驅體會與后續氣體發生 “氣相反應”,生成粉末狀雜質,導致金屬膜出現缺陷。

3. 反應氣體觸發:生成金屬原子層

通入第二種反應氣體(如氫氣、氨氣、氧氣),這些氣體與吸附在基材表面的前驅體分子發生化學反應,例如氫氣會還原前驅體中的金屬離子,生成純金屬原子(如銅原子、銀原子),同時產生揮發性副產物(如有機小分子)。這些副產物會再次被惰性氣體吹掃排出,最終在基材表面留下一層厚度僅為 “原子級”(0.1-0.5nm)的金屬膜。

4. 循環重復:疊加至目標厚度

重復 “前驅體吸附→惰性氣體清洗→反應氣體觸發→惰性氣體清洗” 的循環,每完成一次循環,就會在基材表面增加一層原子級金屬膜。通過控制循環次數,可精準調節金屬膜厚度 —— 例如,若每次循環沉積 0.2nm,要得到 20nm 厚的銅膜,只需重復 100 次循環,誤差可控制在 ±1nm 內,這是傳統工藝無法實現的精度。

(二)工藝核心要素:決定金屬化質量的 “三大關鍵”

要讓原子層沉積在電路板金屬化中穩定應用,需重點控制三大要素,缺一不可:

? 前驅體選擇:兼顧活性與穩定性

前驅體需滿足 “易揮發、易吸附、反應活性高、無毒性” 四大要求。例如,銅金屬化中常用的 Cu (acac)?前驅體,在 150-200℃下即可揮發,且能與氫氣高效反應;而銀金屬化的 Ag (thd) 前驅體,則適合柔性基板的低溫沉積,避免高溫損傷基材。

? 反應溫度控制:適配不同基材特性

電路板基材差異大,FR-4 樹脂耐高溫性較好(可承受 250℃以上),但柔性聚酰亞胺基板的耐高溫上限僅為 200℃。因此,ALD 工藝需根據基材調整溫度 —— 柔性基板采用 100-150℃低溫沉積,剛性基板可提升至 200-300℃,確保前驅體活性的同時,不破壞基材結構。

? 腔室環境:保證沉積純度

反應腔室需維持高真空(10??-10??Pa)和低雜質含量(氧、水含量<1ppm),否則氧氣、水汽會與前驅體反應生成氧化物雜質,導致金屬膜導電性下降。因此,腔室通常配備分子泵、干燥器等設備,實時監控環境純度。

三、原子層沉積電路板金屬化工藝:四大核心優勢

相比傳統的電鍍、PVD 工藝,原子層沉積電路板金屬化工藝在 “精度、兼容性、可靠性” 上形成顯著優勢,完美適配高端電路板的制造需求:

(一)超高均勻性:解決 “復雜結構金屬化難題”

傳統電鍍工藝中,電流在微小通孔或溝槽的邊緣易集中,導致 “邊緣金屬膜厚、中心薄”,甚至出現中心無金屬覆蓋的 “空洞”;而 PVD 通過物理濺射沉積,在深寬比>5:1 的結構中,底部沉積厚度僅為表面的 30%,無法滿足均勻性要求。

ALD 的 “自限制吸附” 特性則徹底解決這一問題 —— 前驅體分子可滲透至微小通孔、溝槽的每一個角落,只要有活性位點就能吸附,最終沉積的金屬膜在不同位置的厚度差異<5%。例如,在孔徑 30μm、深寬比 12:1 的電路板通孔中,ALD 沉積的銅膜厚度均勻性可達 98% 以上,而電鍍工藝的均勻性僅為 60%-70%,這為高密度互聯板(HDI)的 “超細線路 + 微小通孔” 集成提供了可能。

(二)極薄可控:適配 “信號高頻化” 需求

5G、AI 設備的信號傳輸頻率已突破 10GHz,傳統電路板的金屬化層若過厚(如電鍍銅膜厚度通常>1μm),會導致 “信號趨膚效應” 增強 —— 高頻信號僅在金屬表面傳輸,過厚的金屬層不僅浪費材料,還會增加信號衰減和串擾,影響設備性能。

ALD 可精準控制金屬膜厚度在 5-50nm 之間,恰好匹配高頻信號的 “趨膚深度”(10GHz 信號在銅中的趨膚深度約為 2μm,ALD 的超薄金屬層可減少無效金屬用量)。同時,超薄金屬層還能降低線路間的寄生電容,提升信號傳輸速度。例如,某手機廠商采用 ALD 銅金屬化的 HDI 主板,信號傳輸延遲較傳統電鍍工藝降低 15%,滿足 5G 毫米波通信的需求。

(三)低溫兼容:支撐 “柔性電路板” 發展

柔性電路板(FPC)是折疊屏手機、可穿戴設備的核心部件,其基材為聚酰亞胺(PI),耐高溫性較差(長期使用溫度<200℃)。傳統電鍍工藝需在 40-60℃下進行,但后續需高溫(200-250℃)退火處理,易導致 PI 基材收縮、變形;PVD 的濺射溫度雖低,但在柔性基板表面的附著力差,反復彎折后金屬膜易脫落。

ALD 工藝可在 100-150℃的低溫下完成金屬化,無需后續高溫處理,完美適配 PI 基材的特性。同時,ALD 金屬膜通過化學鍵與基材結合,附著力可達 50MPa 以上(傳統 PVD 金屬膜附著力僅為 20-30MPa),經 10 萬次彎折測試后,金屬膜的電阻變化率<5%,遠低于行業 10% 的標準,為柔性電子設備的可靠性提供保障。

(四)高致密性與耐腐蝕性:提升電路板壽命

電路板在使用過程中易受潮濕、化學腐蝕(如汗液、環境中的鹽分)影響,導致金屬化層氧化、腐蝕,進而引發短路或斷路。傳統電鍍銅膜的致密度較低,存在微小孔隙,易被水汽滲透;而 PVD 金屬膜雖致密,但表面易形成氧化層,影響導電性。

ALD 沉積的金屬膜為 “無孔隙” 結構,致密度可達 99.9% 以上,能有效阻擋水汽、鹽分的滲透。同時,通過 ALD 可在金屬膜表面再沉積一層超薄保護層(如 Al?O?、TiO?),進一步提升耐腐蝕性。例如,在濕熱環境(溫度 85℃、濕度 85%)下進行 1000 小時老化測試,ALD 金屬化的電路板腐蝕面積僅為傳統電鍍工藝的 1/10,使用壽命延長 2-3 倍。

四、原子層沉積 vs 傳統工藝:電路板金屬化技術對比

為更直觀體現原子層沉積電路板金屬化工藝的優勢,下表從 “沉積精度”“適用場景”“成本” 等核心維度,與傳統電鍍、PVD 工藝進行對比:

對比維度 | 原子層沉積(ALD) | 傳統電鍍 | 物理氣相沉積(PVD) |

沉積精度(厚度控制) | 原子級(±1nm),均勻性>95% | 微米級(±0.1μm),均勻性 60%-80% | 納米級(±5nm),均勻性 70%-85% |

適用線路寬度 | <10μm(支持超細線路) | >20μm | 10-20μm |

深寬比適應能力 | >15:1(支持深溝槽 / 微小通孔) | <5:1 | 5-10:1 |

基材兼容性 | 廣泛(FR-4、PI、陶瓷均可),低溫兼容 | 有限(主要適用于剛性基材) | 中等(柔性基材附著力差) |

金屬膜附著力 | 強(化學鍵結合,>50MPa) | 中等(機械結合,30-40MPa) | 弱(物理結合,20-30MPa) |

生產成本 | 高(設備單價>1000 萬元,前驅體貴) | 低(設備單價<200 萬元) | 中(設備單價 500-800 萬元) |

產能 | 低(批次處理,每小時<50 片基板) | 高(連續生產,每小時>200 片基板) | 中(批次處理,每小時 80-120 片基板) |

主要應用場景 | 高端 HDI、先進封裝基板、柔性電路板 | 普通剛性電路板、消費電子主板 | 中高端 HDI、半導體封裝引線上 |

五、原子層沉積電路板金屬化工藝:三大核心應用場景

目前,原子層沉積電路板金屬化工藝雖因成本較高暫未大規模普及,但在 “高端化、精細化” 需求強烈的領域已實現商業化應用,成為頭部電子廠商的 “核心競爭力”:

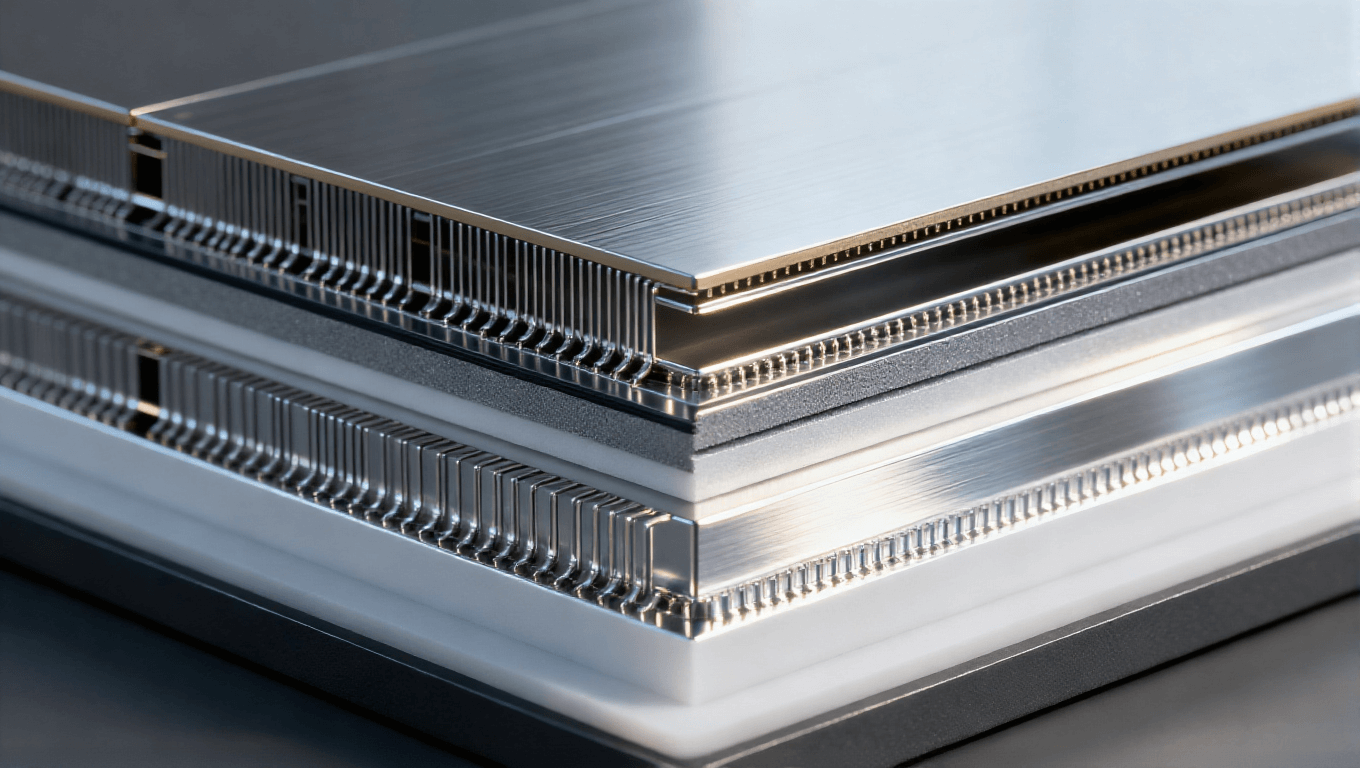

(一)高密度互聯板(HDI):手機、筆記本的 “性能核心”

隨著手機攝像頭從 “單攝” 升級為 “多攝 + 潛望式長焦”,主板需集成更多芯片(如圖像處理器、射頻芯片),線路密度大幅提升 —— 主流旗艦手機的 HDI 主板線寬已縮減至 15μm,通孔孔徑降至 40μm,傳統電鍍工藝難以滿足均勻性要求。

頭部手機廠商(如蘋果、三星)已采用 ALD 銅金屬化工藝制造 HDI 主板:通過 ALD 在 15μm 線寬的線路表面沉積 20nm 厚的銅膜,再疊加電鍍銅層至目標厚度(0.5μm),既保證線路的均勻性,又降低成本。采用該工藝的 HDI 主板,線路間串擾減少 20%,信號傳輸速率提升 10%,同時主板面積縮小 15%,為手機內部節省更多空間。

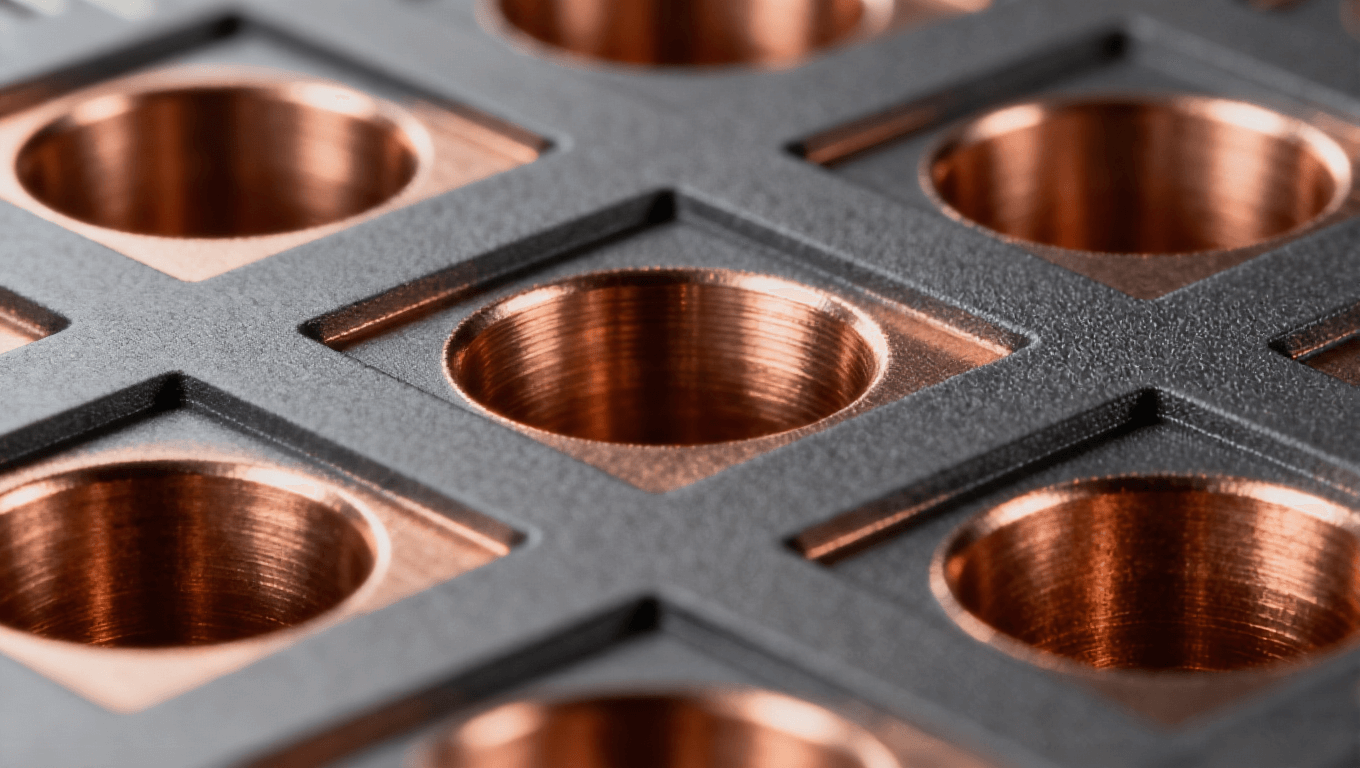

(二)先進封裝基板:AI 芯片的 “導電橋梁”

AI 芯片的算力密度已突破 100TOPS/W,芯片與封裝基板之間的 “互聯點” 數量從數百個增至數千個,互聯間距從 100μm 縮減至 50μm 以下,傳統封裝基板的金屬化工藝(如電鍍鎳金)已無法滿足 “低延遲、高可靠性” 的需求。

先進封裝基板(如 FC-BGA 基板)采用 ALD 工藝進行金屬化:在基板的 “微凸點”(直徑 50μm)表面沉積 10nm 厚的鈦(Ti)過渡層,再沉積 30nm 厚的銅(Cu)導電層,最后電鍍銅至 100μm 厚。ALD 過渡層能提升銅層與基板的附著力,避免微凸點在高溫焊接時脫落;同時,ALD 銅層的高致密性可減少電流遷移,延長 AI 芯片的使用壽命。目前,英偉達 A100、華為昇騰 910 等高端 AI 芯片的封裝基板,均采用 ALD 金屬化工藝。

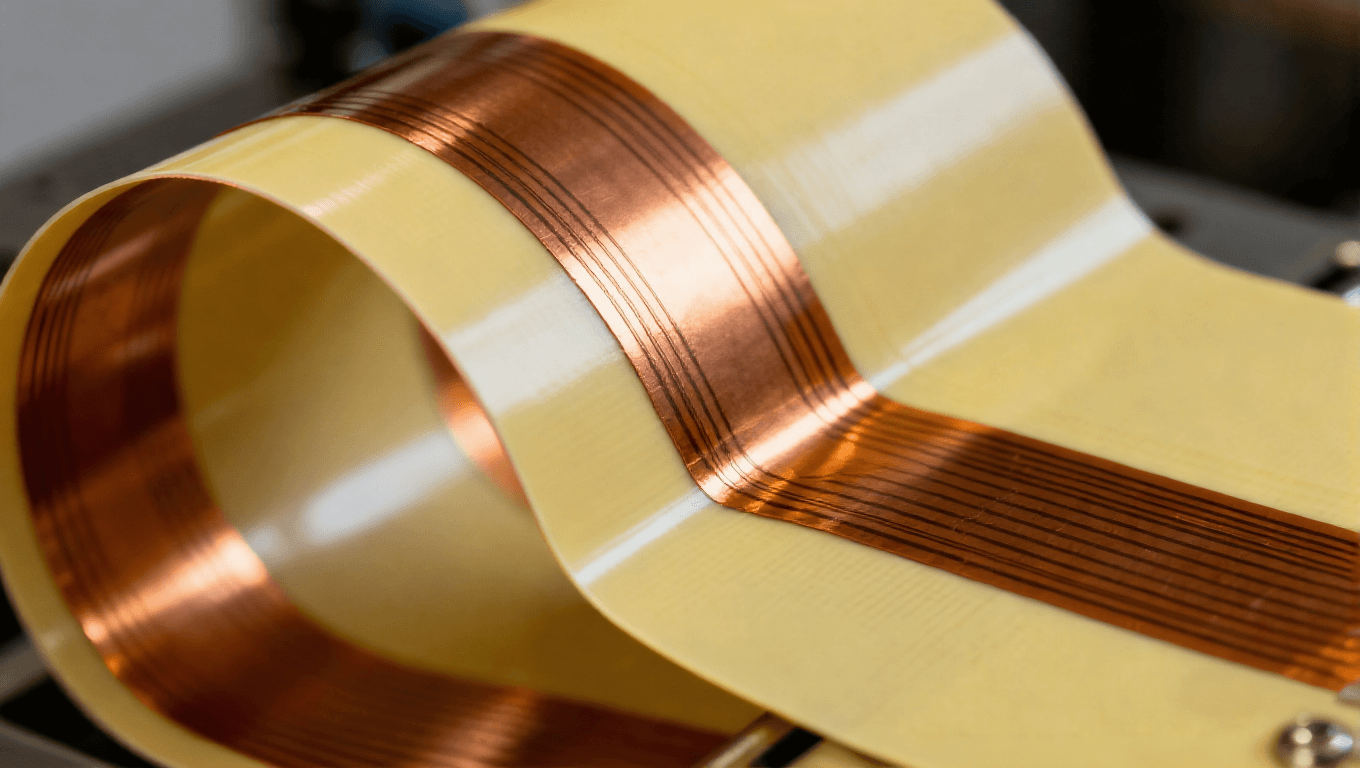

(三)柔性電路板(FPC):折疊屏、可穿戴設備的 “柔性保障”

折疊屏手機的柔性電路板需承受 “反復彎折”(行業標準為 20 萬次彎折無故障),傳統 PVD 金屬化的 FPC 在彎折 10 萬次后,金屬膜會出現裂紋,電阻急劇上升;而電鍍工藝的高溫處理會導致 PI 基材老化,影響柔性。

ALD 工藝為柔性電路板提供了理想解決方案:在 PI 基材表面低溫(120℃)沉積 25nm 厚的銅膜,再通過 “ALD + 電鍍” 復合工藝增厚至 0.3μm。這種復合金屬化層的彎折性能優異 —— 經 20 萬次彎折(彎折半徑 1mm)后,電阻變化率僅為 3%,遠低于行業 8% 的標準。目前,三星 Galaxy Z Fold5、小米 MIX Fold3 等折疊屏手機的柔性電路板,均采用 ALD 金屬化工藝,故障率較傳統工藝降低 60%。

六、原子層沉積電路板金屬化工藝:發展挑戰與未來趨勢

盡管原子層沉積電路板金屬化工藝優勢顯著,但仍面臨 “成本高、產能低” 的挑戰,同時也在技術升級中展現出三大發展趨勢:

(一)當前核心挑戰:成本與產能的 “雙重制約”

? 設備與材料成本高:ALD 設備依賴進口(如芬蘭 Picosun、美國 Cambridge NanoTech),單臺設備單價超過 1000 萬元,是傳統電鍍設備的 5 倍以上;同時,金屬前驅體(如 Cu (hfac)?)的價格為每公斤數萬元,是電鍍液的 10-20 倍,導致單位面積金屬化成本較高。

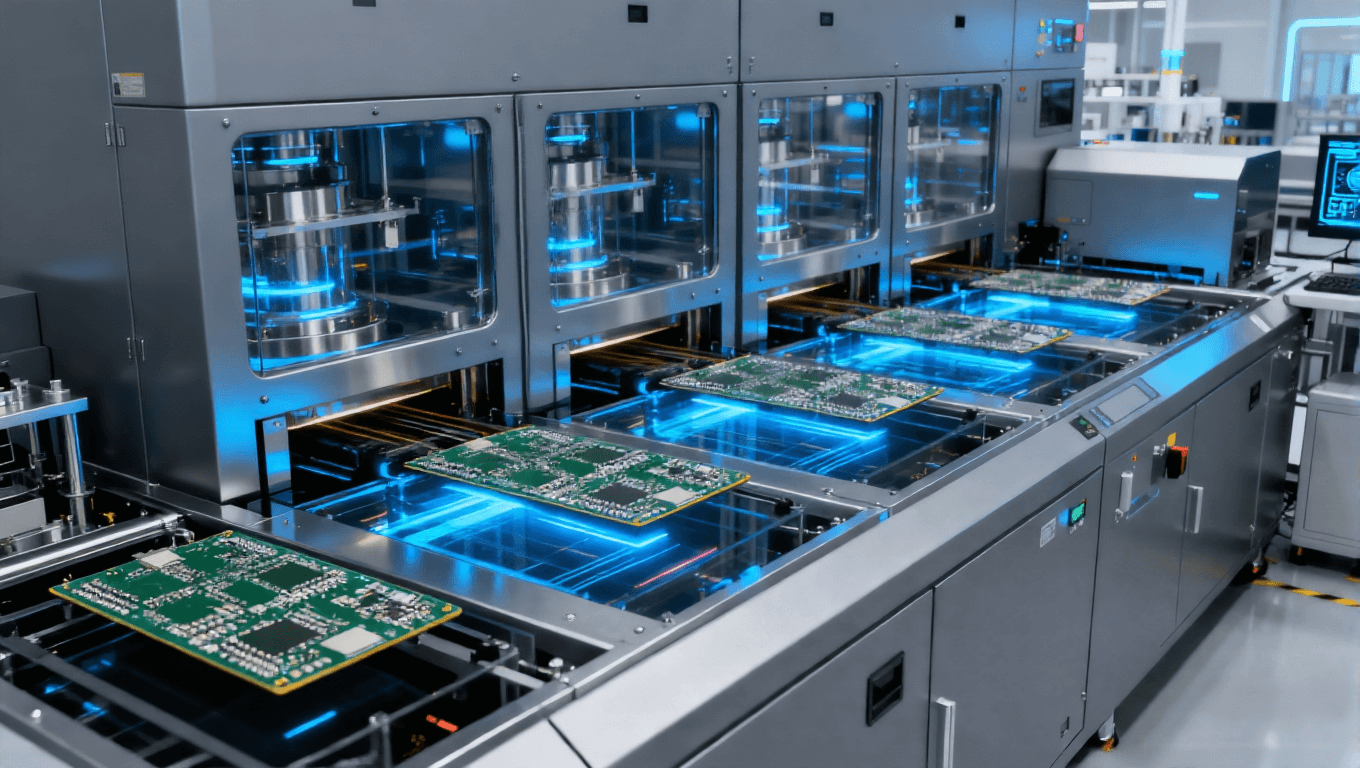

? 產能效率低:ALD 采用 “批次處理” 模式,每批次需完成多次 “吸附 - 清洗 - 反應” 循環,處理一片 6 英寸基板需 30-60 分鐘,而電鍍工藝可連續生產,每小時處理 200 片以上,產能差距顯著。

(二)未來三大發展趨勢

1. 設備國產化與產能提升

國內企業已開始研發電路板專用 ALD 設備,預計 2025 年國產化設備單價可降至 500-800 萬元,成本降低 30%-50%;同時,通過 “多腔室并行處理” 設計,單臺設備產能可提升至每小時 100-150 片基板,逐步接近 PVD 工藝水平。

2. 前驅體國產化與性能優化

國內高校(如復旦大學、清華大學)已研發出低成本銅前驅體(如 Cu (acac)?的國產化替代產品),價格較進口產品降低 40%,且反應活性相當;未來還將開發 “多功能前驅體”,在沉積金屬的同時實現 “防腐蝕、抗遷移” 功能,減少工藝步驟。

3. 與其他工藝的 “復合應用”

為平衡成本與性能,“ALD + 電鍍”“ALD+PVD” 的復合工藝將成為主流:通過 ALD 沉積超薄 “種子層”(5-10nm),保證均勻性和附著力,再通過電鍍或 PVD 增厚至目標厚度,既降低成本,又兼顧性能。例如,在普通 HDI 主板中,采用 “ALD 種子層 + 電鍍增厚” 工藝,成本較純 ALD 工藝降低 60%,同時滿足均勻性要求。

七、結語:原子層沉積 —— 開啟電路板制造的 “原子級時代”

從傳統電鍍的 “微米級控制” 到原子層沉積的 “原子級精度”,原子層沉積電路板金屬化工藝不僅是一項技術升級,更是推動電子制造向 “高密度、柔性化、高可靠性” 發展的核心動力。它解決了高端電路板制造中的 “卡脖子” 難題,為 5G、AI、柔性電子等領域的創新提供了底層支撐。

盡管當前仍面臨成本與產能的挑戰,但隨著設備國產化、前驅體優化、復合工藝的發展,原子層沉積電路板金屬化工藝將逐步從 “高端小眾” 走向 “規模化應用”,成為未來電路板制造的主流技術之一。對于電子制造企業而言,提前布局該技術,將成為搶占高端市場的關鍵競爭力。